応用情報技術者試験 平成30年春 午前問22 解説付き過去問

問題

クロックの立上りエッジで、データを入力の最下位ビットに取り込んで上位方向へシフトし、ストローブの立上りエッジで値を確定する8ビットのシリアル入力パラレル出力シフトレジスタがある。

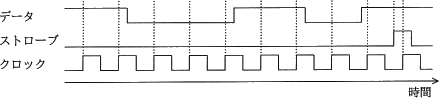

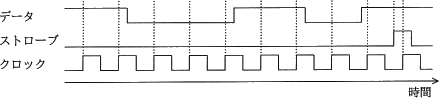

各信号の波形を観測した結果が図のとおりであるとき、確定後のシフトレジスタの値はどれか。

ここで、数値は16進数で表記している。

正解

解説

この問題は、シリアル入力をクロック信号に同期して最下位ビットから順に読み取り、8ビットのシフトレジスタに格納し、ストローブ信号の立上りで値を確定する動作について理解しているかを問うものです。図の波形から、データの取り込みタイミングと順序を正確に把握することが重要です。

- シフトレジスタの動作

このシフトレジスタは、クロック信号の立上りエッジごとに1ビットずつデータを最下位ビットに取り込み、既存のビット列を1ビットずつ上位方向へシフトします。

8ビット構成のため、連続して8回のクロック立上りがあれば、8ビットのデータがすべて格納されます。

最終的なレジスタの値は、ストローブ信号の立上りエッジで確定されます。 - 波形図に基づくビットの取得

図から、クロックの立上りエッジの直前にデータ入力線が示している値を1ビットずつ読み取っていきます。取得されたビットは、以下の順でシフトレジスタに取り込まれていきます:

右から順に並べると、「1 → 0 → 0 → 0 → 1 → 1 → 0 → 1」の順で入力され、最終的なレジスタの状態は10001101(2進数)となります。 - 2進数から16進数への変換

得られた2進数「10001101」を4ビットずつ区切って16進数に変換します。

上位4ビット「1000」は「8」、下位4ビット「1101」は「D」なので、全体で8Dとなります。

したがって、確定されたシフトレジスタの内容は16進数で 8D となります。